本文共953字

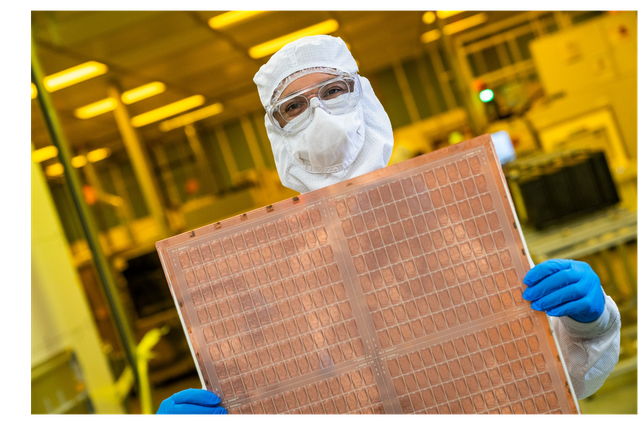

英特爾21日於創新日活動宣布,與台積電(2330)攜手,打造全球首款符合小晶片(Chiplet)「互連產業聯盟(UCIe)」標準的多晶片封裝晶片,當中包含英特爾與台積電各自生產的IC,開啟全球「晶片製造的新時代」。

業界分析,小晶片架構設計有助降低IC設計與系統客戶成本,由於整合不同製程的晶片,並透過先進封裝技術實現差異化堆疊,實現更多元晶片應用,已成為半導體業界新顯學,吸引大咖爭相投入。

隨著英特爾與台積電完成首款符合UCIe標準的多晶片封裝晶片,意味摩爾定律獲得延續成為可能,讓AI、高速運算等應用更能蓬勃發展,開創半導體新動能。

英特爾、台積電、三星等指標廠2022年3月號召超微(AMD)、高通、安謀(Arm)、日月光、Meta等涵蓋晶圓製造、IC設計、封裝測試、雲端、網路服務業的產業大咖籌組UCIe,目標建立晶片到晶片(die-to-die)的互連標準,並促進開放式小晶片生態系,短短一年半時間,聯盟成員已逾120家。

英特爾與台積電更領頭,強強聯手開發出符合相關規範的晶片,開啟全球「晶片製造的新時代」。

根據英特爾的定義,UCle標準是界定封裝內小晶片之間互連的開放性規範,允許來自各家廠商的小晶片可以共同運作,相關設計預期可因應各式AI工作負載的擴張需求。UCle標準最先是發布1.0版規範,今年8月進一步發布1.1版規範,增加對於車輛相關應用的支援等。

英特爾此次攜手台積電,打造的全球首顆符合UCIe標準的多晶片封裝晶片,由以Intel 3製程製造的英特爾UCle IP晶片,以及由台積電N3E製程節點所製造的Synopsys UCIe IP晶片組成,並採用英特爾EMIB先進封裝技術。

英特爾強調,這款測試晶片展現出台積電、Synopsys和英特爾晶圓代工服務對UCle建構公開標準化晶片生態系的支持。

業界人士分析,在先進製程逐漸微縮的同時,在單一封裝內,基於模組化架構,納入不同製程、用途各異的小晶片,被視為是節省晶片成本並繼續延伸摩爾定律的方法之一。因此,不同廠商生產的小晶片,如何能夠有效互連運行,就成為後續晶片發展的重要課題。

英特爾執行長基辛格預測,下一波摩爾定律將伴隨多晶片封裝而起,如果開放標準可以更進一步增進IP整合,時程可望再縮短。

延伸閱讀

※ 歡迎用「轉貼」或「分享」的方式轉傳文章連結;未經授權,請勿複製轉貼文章內容

留言