本文共2231字

全球產業數位化,數位資料規模攀升,加上AI技術興起,全球對資料處理、大數據分析與AI應用的需求快速增長,間接提高對支援高效能運算(HPC)與AI運算的硬體裝置及晶片要求。以雲端資料中心伺服器來說,HPC與AI運算需求下,需要搭配升級的晶片包含作為運算核心的中央處理器(CPU)與圖形處理器(GPU)、伺服器基板管理晶片(BMC)、電源管理晶片(PMIC)、高速傳輸晶片,以及記憶體等。

其中,記憶體除用於長期儲存資料、屬於非揮發性記憶體的NAND Flash固態硬碟(SSD),也包含用於即時高速運算暫存資料、屬於揮發性記憶體的靜態隨機存取記憶體(SRAM)與動態隨機存取記憶體(DRAM)。

記憶體在晶片運算過程中的主要作用,是暫存運算過程中的中間值或參數。傳統的暫存用記憶體可區分為晶片內部的快閃(Cache)記憶體與外部連接的DRAM。隨著運算效能持續提升,晶片對內部與外部記憶體的容量與資料存取速率要求提高,特別是內部Cache記憶體。在封裝的空間尺寸有限下,將小晶片(Chiplet)透過先進封裝在單一晶片內形成更高密度的堆疊整合,成為提高晶片內部記憶體容量的重要選項。

先進封裝技術發展針對晶片運算效能與功能持續提升的需求,透過中介層、矽穿孔與微凸塊等技術達成2.5D/3D的小晶片堆疊,使業者能在更小空間內達成更多運算單元與晶片功能整合。超微(AMD)的Ryzen 7 5800X3D晶片就是記憶體小晶片與CPU堆疊整合的例子:透過在CPU上方堆疊64MB的SRAM記憶體小晶片,將CPU原本32MB的Cache記憶體擴充為96MB,使CPU運算效能提升15%。

不過,用於HPC或AI運算的高階GPU晶片,如輝達(NVIDIA)的H100與超微的MI300,其主要運算架構是以GPU運算核心搭配可快速大量存取傳輸資料的高頻寬記憶體( HBM),二者透過先進封裝技術,也就是台積電的CoWoS 2.5D封裝技術在中介層上整合連接。

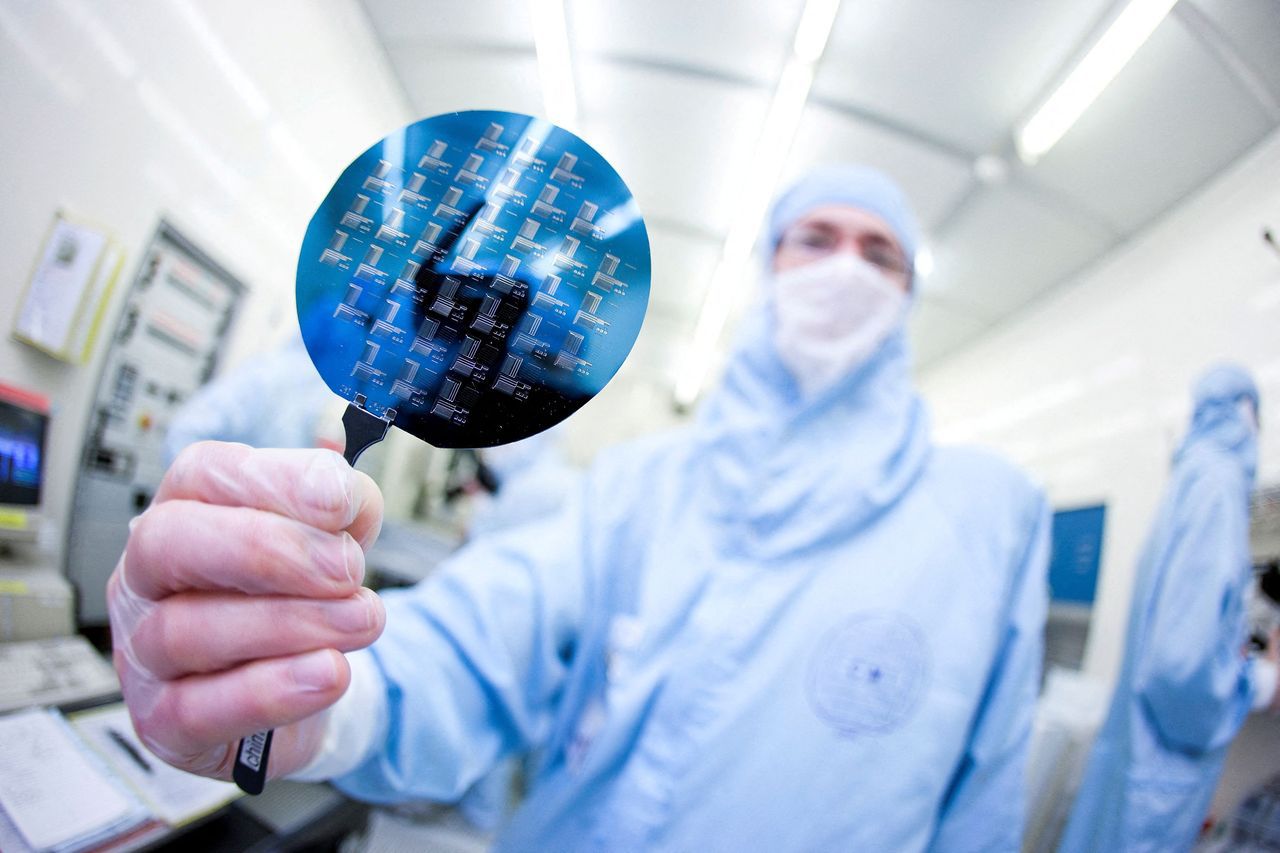

HBM是超微與南韓記憶體大廠SK海力士、我國聯電、日月光等夥伴合作開發,SK海力士在2015年量產第一代HBM(HBM1),導入超微Radeon Rx300 GPU晶片。隨後南韓與記憶體大廠Samsung Electronics與Micron Technology也投入HBM開發。其主要結構是由多層DRAM記憶體小晶片形成的高容量記憶體垂直堆疊,最下層是HBM的控制晶片。堆疊中上一層DRAM與下一層DRAM間的訊號透過微凸塊連接,而上一層DRAM的訊號可穿過下一層DRAM的矽穿孔與更下層的DRAM甚至最下層的控制晶片連接,再向下傳遞至基板。垂直堆疊的短距離確保層與層間的訊號傳輸快速且耗能低,間接提升運算效能。

在CoWoS架構下,GPU運算核心可搭配多個HBM堆疊。目前全球已發展到HBM3的最新規格,在HBM堆疊數、垂直堆疊層數及層間訊號連接通道數都有增加;如從HBM2到HBM3,堆疊數可從八個增至16個,有效提升記憶體的資料容量與存取傳輸速率。

HBM主要是搭配GPU這類高運算效能晶片,本身主要結構採用3D堆疊的先進封裝製作,再以CoWoS先進封裝與GPU運算核心整合,形成完整的GPU晶片。若非GPU採用7奈米以下先進製程製作,是屬於高單價產品,要以先進封裝整合HBM的晶片生產成本是難以承受。在超微Ryzen 7 5800X3D晶片的例子中,CPU上方堆疊SRAM小晶片,為提高記憶體容量,也需以先進製程製作SRAM,成本高昂。

針對智慧物聯網(AIoT)應用所需中等算力需求,有半導體業者提出非先進製程運算晶片搭配客製化DRAM記憶體的解決方案,將記憶體與運算晶片以3D封裝垂直堆疊。所謂的客製化DRAM記憶體,是根據運算晶片的電路與內連線的接觸電極分布,設計出DRAM晶片的電路與資料存取傳輸通道位置,使運算晶片與垂直堆疊的DRAM小晶片之間能有高效率的資料存取傳輸,以提升運算效能。運算晶片是以AIoT應用所需的單晶片(SoC)或特殊應用晶片(ASIC)為主,而DRAM高於SRAM的記憶體密度,讓DRAM小晶片在不採用先進製程下可擁有相當於SRAM小晶片的容量,也是成本優勢。

國內有記憶體業者與晶圓代工業者、封測業者、IC設計業者合作,構建解決方案平台,依照應用需求,完成ASIC、DRAM以及二者封裝連接與散熱等需求的完整設計。無論是ASIC與DRAM都採用成熟製程製作,相較HBM、SRAM與先進製程運算晶片的組合,成本降低,可因應應用開發業者對成本結構的要求。

因應日漸增加的AI應用,記憶體以小晶片或HBM等不同的樣態,可透過先進封裝技術與運算晶片形成單一晶片封裝,支持不同類型的運算需求,也促成國內半導體產業鏈跨領域多元整合的生態體系發展。

(作者是資策會MIC資深產業分析師)

小晶片是什麼?

小晶片(Chiplet)是一個微型集成電路(integrated circuit,IC),包含明確定義的功能子集。它被設計為與單個封裝內插器上的其他小晶片結合在一起。一組芯粒可以在混合搭配「樂高式」堆疊組件中實現。(維基百科)

高頻寬記憶體優勢

高頻寬記憶體(HBM)相比較DDR4或GDDR5而言,高頻寬記憶體以更小的體積、更少的功率達到了更高的頻寬。這是由堆積至多八塊DRAM裸晶(即三維積體電路)的方式達成的,此方法搭載了通過矽穿孔(TSV)及微突起相連接的可選基 底裸晶,附帶記憶體控制器。(維基百科)

※ 歡迎用「轉貼」或「分享」的方式轉傳文章連結;未經授權,請勿複製轉貼文章內容

留言